Zé80, O computador

Projeto pessoal, iniciado no segundo semetre de 2017, com o intuito de projetar e construir um computador básico baseado no microprocessador Z80, famoso nas décadas de 80 por ser o principal processador usado nos primeiros Personal Computers disponíveis para o grande público. Este projeto se integra com o projeto do gravador de memória EPROM pois, a princípio, a memória deste pequeno computador sera justamente uma 27C512. Ele contara apenas com uma ROM no primeiro protótipo.

Usando a arquitetura do 8080, o microprocessador Z80 ou para os íntimos, Zé80 possui barramento de 8 bits de dados, 16 bits de endereços, pode trabalhar com dispositivos I/O e ter um clock máximo de 20MHz (antes que perguntem, não, ele não rodará Minecraft em 60fps!). O objetivo deste projeto é construir um computador básico para que alunos de disciplinas de Álgebra Booleana e Técnicas de Programação, onde aprendem arquitetura básica de computadores em um simulador (LogiSim) e aprendem assembly para computadores da família x86, respectivamente, e muitas vezes devido a falta de uma visualização mas "física" do computador simulado, a curva de aprendizado pode possuir uma derivada um tanto quanto pequena, programar um computador tão rudimentar usando o assembly aprendido pode ser motivador. A idéia é que as trilhas de dados e endereços fiquem visíveis na placa para facilitar a compreensão do que é um barramento, que seja possível controlar a velocidade do clock para conseguir acompanhar o ciclo de fetch/decode/execute, e que seja possivel acompanhar tabém os dados que circulam nos barramentos em todos os momentos.

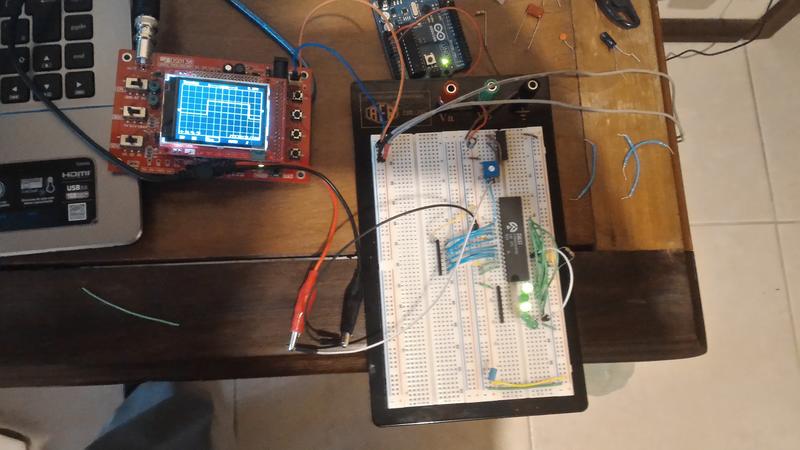

Imagem do primeiro teste do clock, usando um osciloscópio

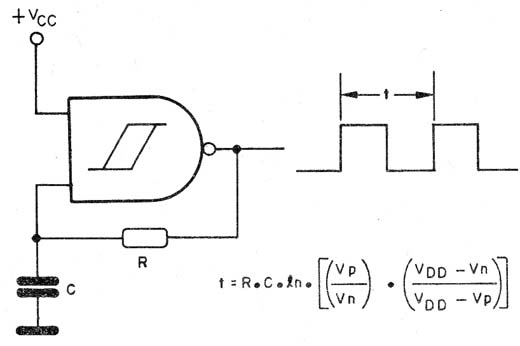

O clock foi implementado usando um chip da família CMOS 40XX, o 4093, trata-se de um CI com 4 portas NAND Schmitt-Trigger, onde para este clock utilizamos apenas uma delas, um capacitor, um resistor e um trimpot (para regular a velocidade do clock), formando o seguinte circuito:

Circuito gerador de clock

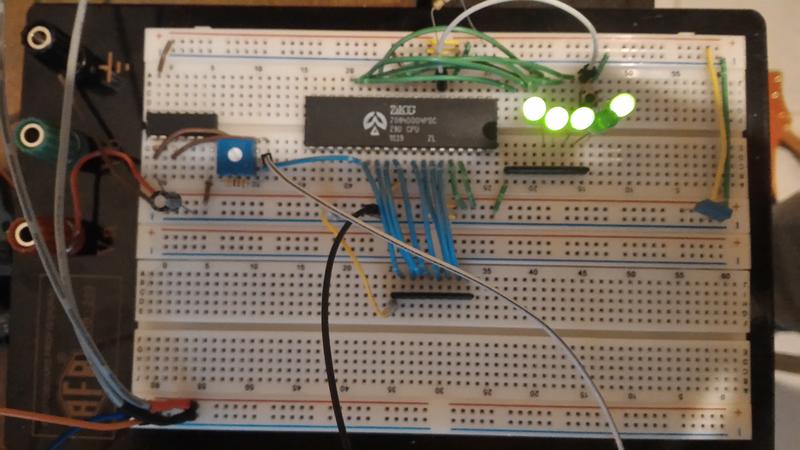

O circuito utilizando o z80 e este clock foi montado na protoboard e testado aterrando-se o barramento de dados para que o processador executa-se apenas operaçoes do tipo NOP, assim veriamos o feedback visual dos leds colocados no barramentos de endereço o qual a cada ciclo o microprocessador incrementaria o contador de posição da memória. Este feedback por momento é em binário onde leds apagados representam 0 e acesos representam 1. Para evitar muitos fios, resolvi utilizar apenas os 5 bits menos significativos do barramento de endereços nesse teste:

Os leds representam os 5 bits menos significativos do endereço de memória acessado pelo microcontrolador

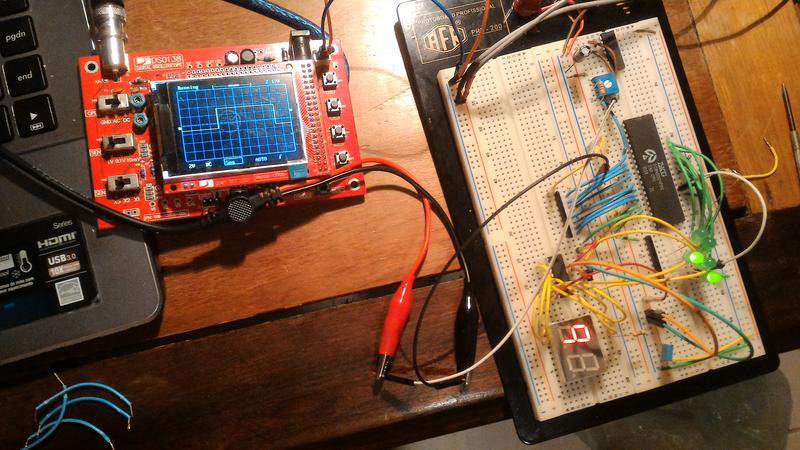

O teste seguinte foi o de usar um conversor binário para decimal 4511 que implementa internamente um circuito combinacional muito útil para converter a representação binária para números decimais em displays de 7 segmentos. Essa seria outra questão interessante de ser citada no projeto pois é uma aplicação clássica de circuitos combinacionais e mapas de Karnaugh aprendidos também em Álgebra Booleana. O teste feito utilizou apenas os 3 primeiros bits do barramento de endereços apenas para entender o funcionamento do CI e planejar o seu uso.

Display de 7 segmentos representando o endereço de memória correspondente aos 3 primeiros bits do barramento de endereços

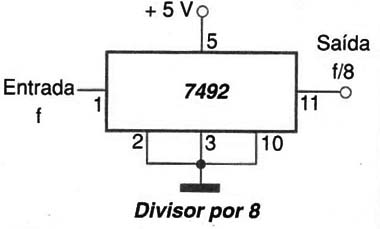

Apesar de querer deixar explícito cada uma das trilhas dos barramentos de dados achei interessante em determinado momento na placa, para reduzir o número de trilhas na placa e para demonstar uma organização tambem usada em computadores reais, usar um par MUX/DEMUX para o barramento de dados, a fim de possivelmente tentar entender como funcionaria multiplexadores e que eles seriam usados de uma forma semelhante a essa em determinadas arquiteturas de computadores. Para isso projetei uma simplificação que apesar de diminuir o clock e consequentemente a taxa de cálculos por segundo tornaria mais didático o entendimento do mesmo no hardware: Inicialmente colocariamos o clock original em um CI divisor por 12, o 7692 na configuração divisor por 8:

Circuito do divisor por 8

O saida deste chip, ou seja, o clock com um período 8 vezes maior seria o clock forncido ao microcontrolador e o clock original, 8 vezes maior, fornecido ao multiplexador, de forma que a cada ciclo de clock do processador ele consiga ter enviado os 8 bits de dados entre o MUX e o DEMUX. Sendo assim, o fato da multiplexação "transparente"ao microprocessador. Existem outras formas de fazer isso usando portas especificas do z80, mas por fins didáticos a decisão de projeto a princípio é essa. O CI usado para implementar o conjunto MUX/DEMUX é o CD4511.O teste foi um sucesso e a multiplexação do barramento foi completamente transparente para o microcontrolador. Outro ponto interessante é citar que este tipo de BUS utilizado é semelhante ao conhecido protocolo Paralelo/Serial.

Este projeto ainda esta em seus primeiros passos, sendo que o último teste feito foi integrando a memória 27C512 ao conjunto, porém devido ao gravador ainda estar em desenvolvimento, não pude testar a leitura de dados. A medida que o projeto for avançando, atualizarei esta página.

EXTRA: Agradecimento ao professor Siang Wun Song, por ter fornecido um material de estudos importantíssimo para o desenvolvimento deste projeto, um computador muito semelhante ao que estou tentando implementar, no qual farei engenharia reversa para entender seu funcionamento. A medida que novas descobertas forem feitas postarei nesta pagina ou em outra dedicada apenas para o procedimento.